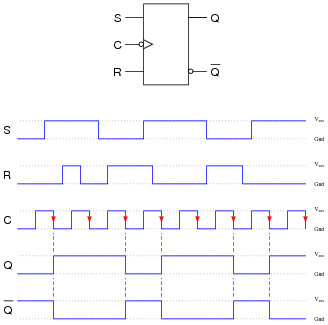

Applied Sciences | Free Full-Text | Voltage-Controlled Spin-Orbit-Torque-Based Nonvolatile Flip-Flop Designs for Ultra-Low-Power Applications

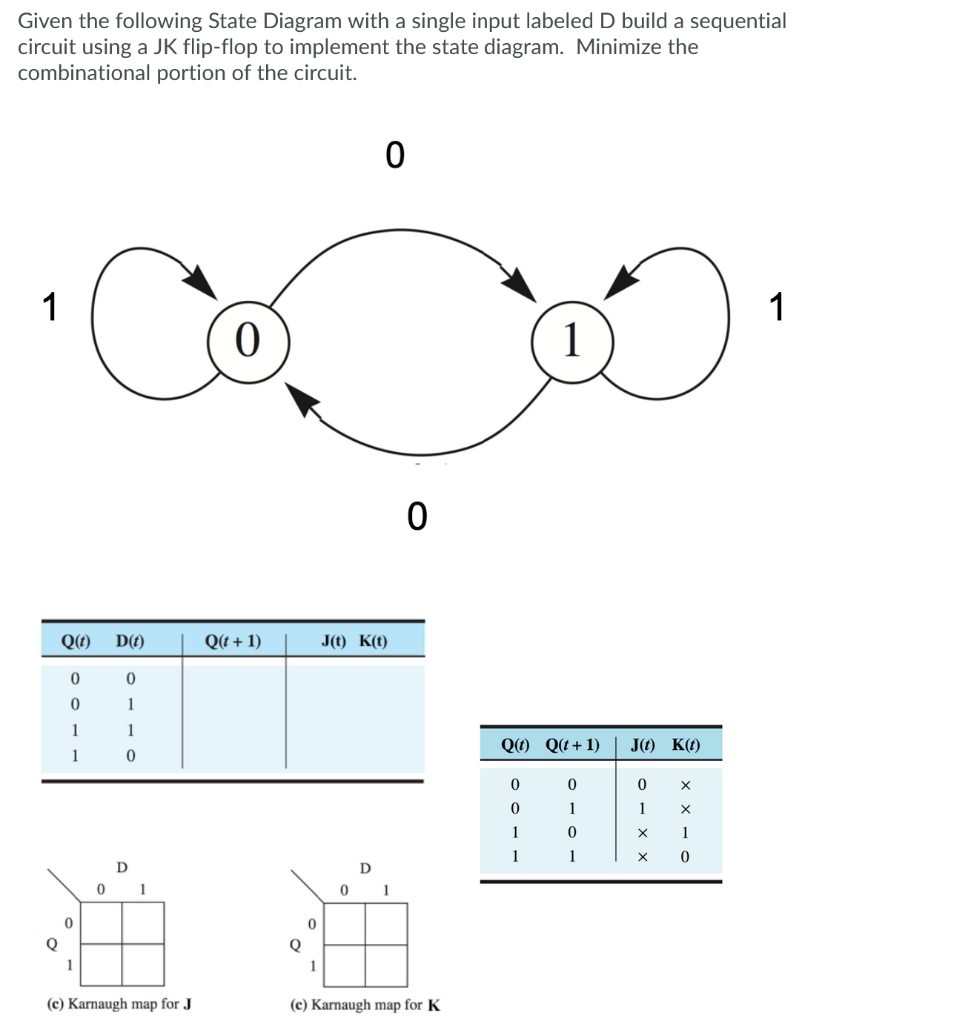

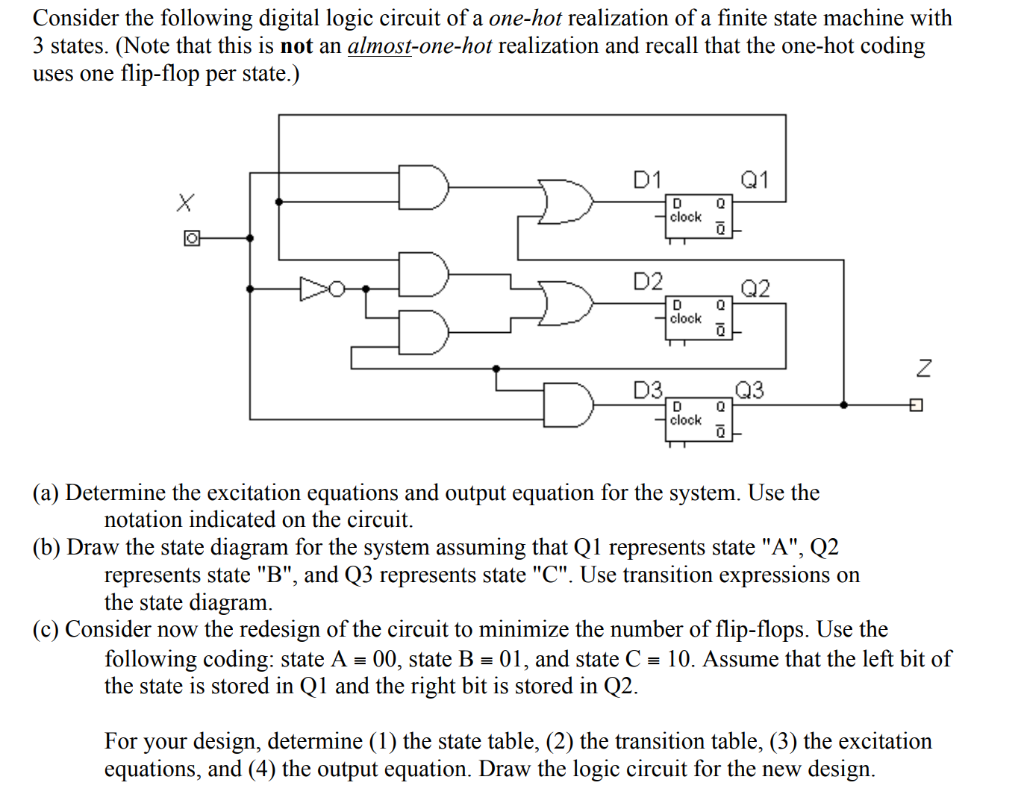

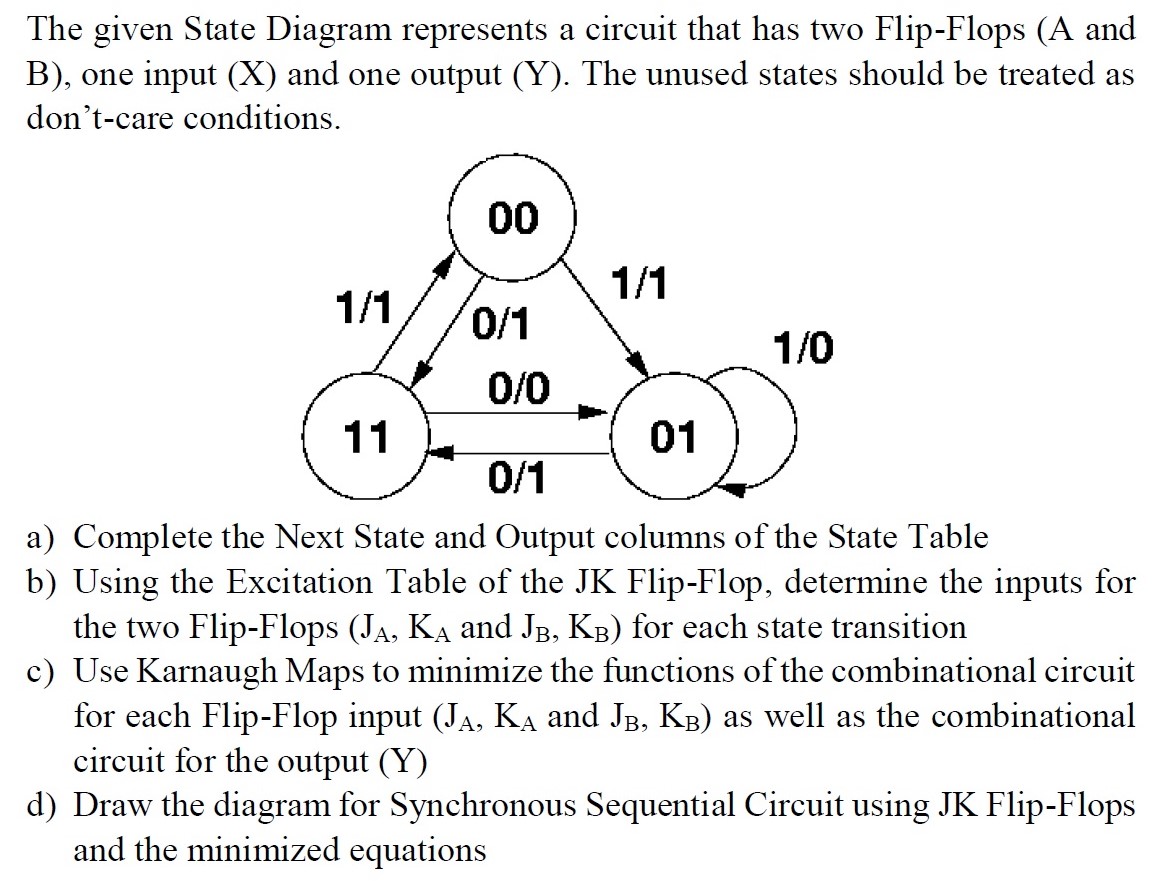

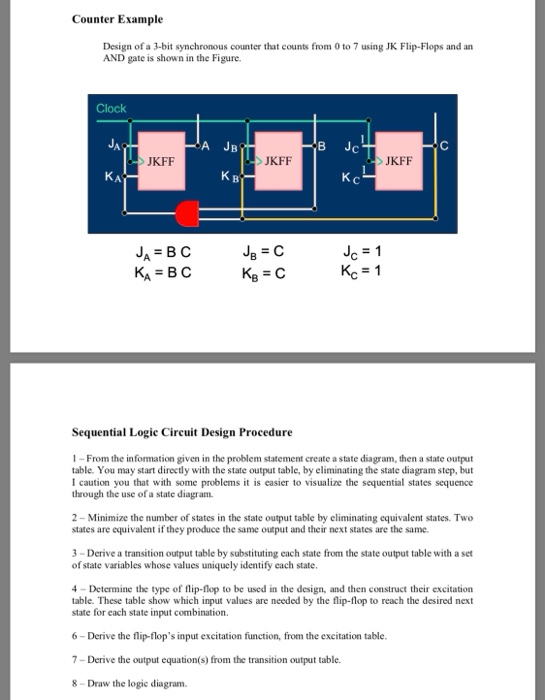

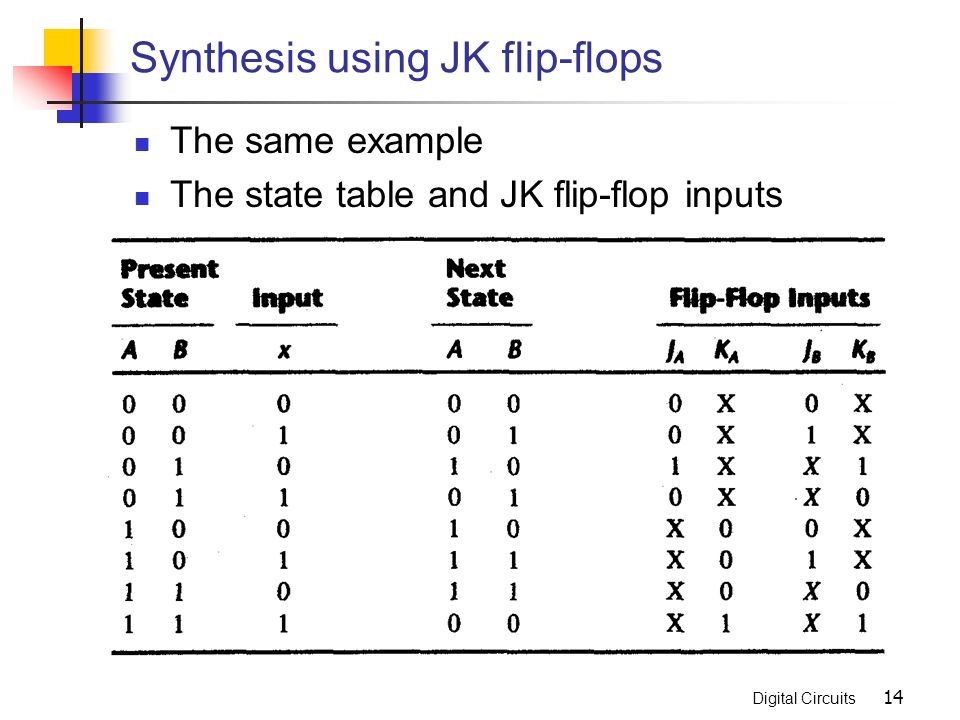

Digital Circuits State Reduction and Assignment State Reduction reductions on the number of flip-flops and the number of gates a reduction in the. - ppt download